摘要:

2.1.2 两级放大器的频率响应 a56爆大奖在线娱乐们现在开始研究补偿电容\(C_c\)对频率响应的影响,补偿电容会在一个频率点开始引发增益幅度的减小,但仍在一个远低于单位增益频率的频点,对应于很多应用的中频点。a56爆大奖在线娱乐们使用一些简化假设,首先忽略除了补偿电容\(C_c\)以外的所有电容,其次a56爆大奖在线娱乐们认为电阻\(R_c\)不 阅读全文

摘要:

2.1.1 两级放大器的增益 两级放大器是历史悠久且流行的放大器设计方案。当设计良好时,两级放大器的性能非常接近使用了Cascode增益级的设计,并且更适合驱动阻性负载。岂能提供高增益和高输出摆幅,使得其再晶体管本征增益和供电电压受限的现代CMOS工艺下成为a56爆大奖在线娱乐非常重要的电路。同时,它也可以作为其他 阅读全文

摘要:

1.4 差分对增益级 MOS集成电路放大器经常使用差分对作为输入。为了实现差分输入,几乎所有的放大器都使用晶体管差分对。如下图所示,一个差分对共同使用一个偏置电流源,晶体管\(Q_1\)和\(Q_2\)大小相同,并偏置在相同的直流栅电压下。 差分对的低频小信号模型如下图所示,为了简化分析,a56爆大奖在线娱乐们暂时忽 阅读全文

摘要:

### 1.3.2 增益提升 之前在电流镜章节提到过应用放大器来增加电流镜输出阻抗,同样的技术被用于增加Cascode增益级的输出阻抗,如下图所示: 中,有一个n沟道共源极管子\(Q_1\)和一个n沟道共栅极管子\(Q_2\),这种结构也被称作 阅读全文

摘要:

### 1.2.3 共栅放大器 带有有源负载的共栅级放大器如下图所示,一般这种结构用于当输入阻抗需要是一个小阻值时。例如,如果需要一个$50\Omega$的输入阻抗来匹配一个$50\Omega$的传输线。另a56爆大奖在线娱乐共栅放大器的常见用于是用在输入信号为电流的放大器的第一阶,在这种情况下为了确保所有的电流信 阅读全文

摘要:

### 1.2.2 共漏放大器(源极跟随器) 另一个电流镜的常见应用时为源极跟随器提供偏置电流,在下图的例子中,$Q_1$为源极跟随器,$Q_2$为给$Q_1$提供偏置电流的有源负载,这个结构一般用于电压缓冲器,因此也被称作源极跟随器。因为输入和输出节点分别在栅极和源极,漏极作为小信号地,这个结构同 阅读全文

摘要:

### 1.2.1 共源放大器 基本电流镜的一个常见用途时用于单管放大器的有源负载,如下图所示,共源放大器是当需要高输入阻抗时最常见的增益级。 此处一个n沟道的共源级放大器以一个p沟道的电流镜作为有源负载提供驱动晶体管的偏置电流。通过使用有源负载来为驱动管子所需要的偏置电流。通过使用有源负载,一个高 阅读全文

摘要:

1.1.7 带有输出阻抗增强的宽摆幅电流镜 下图的结构在[Gatti, 1990],[Coban, 1994; Martin, 1994]中被提出和使用,与[Säckinger, 1990]的输出阻抗增强电流镜结构很像,除了一个二极管接法的晶体管被加在共源级增强放大器前作为电压转换器。 在输出光,电 阅读全文

摘要:

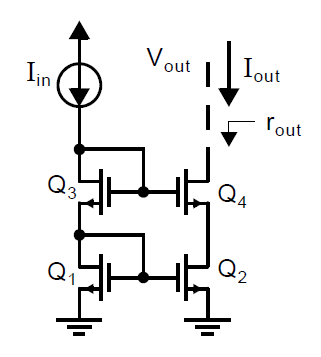

### 1.1.6 输出阻抗增强电流镜 另a56爆大奖在线娱乐常用的Cascode电流镜的变种是输出阻抗增强电流镜,a56爆大奖在线娱乐简单电路形式如下图所示:  这是一个使用 阅读全文

摘要:

### 1.1.3 Cascode电流镜 Cascode电流镜是a56爆大奖在线娱乐高输出阻抗电流镜,其基本结构如下图所示:  首 阅读全文

摘要:

### 1.1.2 源极退化电流镜 简单电流镜可以仅通过两根晶体管实现,其作为电流源的输出阻抗为$r_{ds2}$,为了进一步增加输出阻抗,可以使用a56爆大奖在线娱乐源极退化电流镜,下图暂时了源极退化电流镜的结构。 ,当时的主要思路还是停留在怎么把计算的logic和DRAM做到一起,受限于存储器工艺和逻辑工艺的不兼容问题,这方面的研究进展并不是很顺利。同时m 阅读全文

摘要:

## SystemVerilog总结 过了两个月的时间,把这本《SystemVerilog for Design (Edition 2)》基本上读完了。对SystemVerilog也建立了一些认识。 本书一共十二章,除去第一章是比较笼统的介绍,最后两章主要是设计实例以外,第二章到第十章都是很干货的语 阅读全文

摘要:

SystemVerilog for Design Edition 2 Chapter 10 SystemVerilog extends the Verilog language with a powerful interface construct. Interfaces offer a new p 阅读全文

摘要:

SystemVerilog for Design Edition 2 Chapter 9 This chapter presents the many enhancements to Verilog that SystemVerilog adds for representing and worki 阅读全文